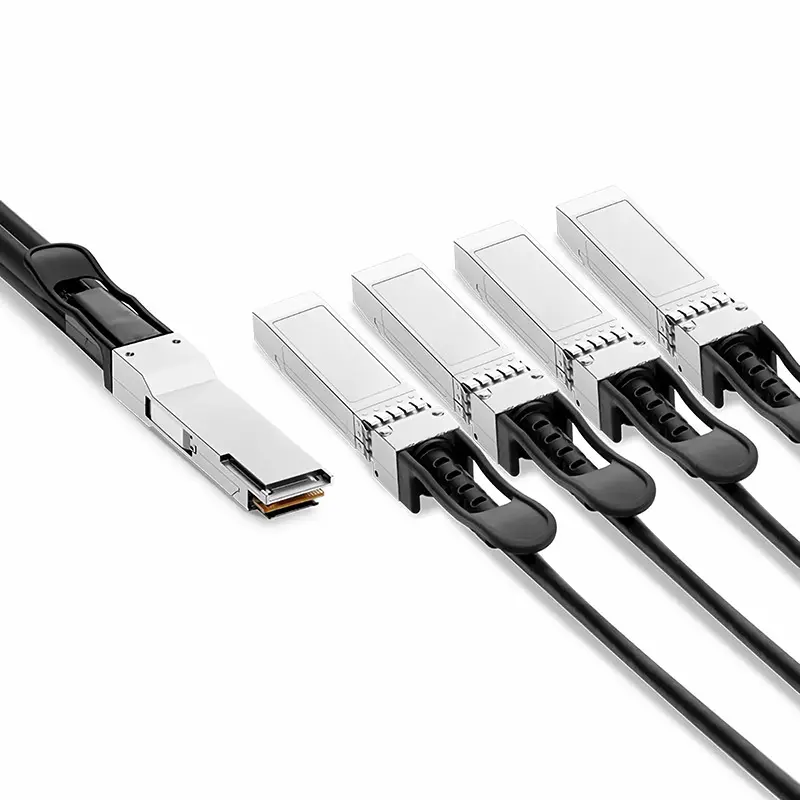

200G QSFP56 to 4x50G SFP56 Passive DAC Breakout

Description

This Farsince breakout assembly converts one QSFP56 200G port into four independent 50G SFP56 copper links over a passive twinax harness. The host side carries four 50G PAM4 lanes and maps each lane to a dedicated SFP56 plug, enabling efficient distribution of a 200G uplink to multiple 50G endpoints. It is suited for in‑rack leaf/spine architectures, top‑of‑rack switch‑to‑server connections, GPU/AI clusters and storage networks where short‑reach, deterministic performance is required.

The passive design introduces virtually no latency and requires no external power, while controlled‑impedance copper pairs and robust shielding maintain low insertion loss and crosstalk. A 35 mm minimum bend radius supports tidy routing in dense racks, and pull‑tab latches simplify tool‑free service. The cable follows QSFP56/SFP56 MSA mechanics and IEEE 802.3cd electrical specifications for broad interoperability. Farsince offers vendor coding, length and labeling options, and provides batch testing documentation to support volume deployment and maintenance.

Specifications

- Product Type: 200G to 4×50G Passive Direct Attach Copper Breakout

- Host Interface: QSFP56, 4×50G PAM4

- Device Interface: 4× SFP56, 50G PAM4 each

- Lane Mapping/Modulation: 4×50G PAM4 to 4×50G PAM4

- Data Rate: 200 Gbps aggregate; 50 Gbps per channel

- Wire Gauge: 26 AWG

- Cable Structure: Shielded twinax harness, passive copper

- Minimum Bend Radius: 35 mm

- Power Consumption: ≤0.1 W per end (for ID)

- Operating Temperature: 0 to +70°C

- Installation: Hot‑pluggable connectors with pull‑tab latches

- Compatibility: IEEE 802.3cd 200GBASE‑CR4/50GBASE‑CR; QSFP56 & SFP56 MSA; SFF‑8636/8472 memory map

- Compliance: RoHS, REACH

- Customization: Vendor coding, length, labeling, and test reports